## Hardware Support for Unbounded Transactional Memory

by Sean Lie

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology

May 7, 2004

© Massachusetts Institute of Technology 2004. All rights reserved.

The author hereby grants to M.I.T. permission to reproduce and distribute publicly paper and electronic copies of this thesis and to grant others the right to do so.

| Author       |                                                           |

|--------------|-----------------------------------------------------------|

|              | Department of Electrical Engineering and Computer Science |

|              | May 7, 2004                                               |

|              |                                                           |

|              |                                                           |

| Certified by |                                                           |

|              | Krste Asanovic                                            |

|              | Thesis Supervisor                                         |

|              |                                                           |

|              |                                                           |

| Accepted by  |                                                           |

|              | Arthur C. Smith                                           |

|              | Chairman, Department Committee on Graduate Theses         |

### Hardware Support for Unbounded Transactional Memory

by

#### Sean Lie

Submitted to the Department of Electrical Engineering and Computer Science

May 7, 2004

In partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

In this thesis, I propose a design for hardware transactional memory where the transaction size is not bounded by a specialized hardware buffer such as a cache. I describe an unbounded transactional memory system called UTM (unbounded transactional memory) that exploits the perceived common case where transactions are small but still supports transactions of arbitrary size. As in previous hardware transactional memory systems, UTM uses the cache to store speculative state and uses the cache coherency protocol to detect conflicting transactions. Unlike previous hardware systems, UTM allows the speculative state to overflow from the cache into main memory, thereby allowing the transaction to grow beyond the size limitation of the cache. The clean semantics of UTM allow nested transaction support, nontransactional instructions, immediate aborts, a processor snapshot, and context-switching support; all features not found in previous hardware transactional systems. UTM was implemented in a detailed simulator, and experimental results show that it can be integrated with existing hardware straightforwardly while still performing better than conventional synchronization techniques.

Thesis Supervisor: Krste Asanovic Title: Associate Professor, MIT CSAIL

## Acknowledgments

Many of the ideas presented in this thesis were developed in collaboration with Krste Asanovic, Charles E. Leiserson, and Bradley C. Kuszmaul. Also, initial ideas were developed with the help of Marty Deneroff and Steve Miller from Silicon Graphics, Incorporated.

In particular, I would like to thank Krste for being a dedicated advisor. I also want to thank Charles for helping me develop my writing and presentation skills.

The compiler aspects of the evaluation were handled by C. Scott Ananian. I would also like to thank Scott for helping me understand his software transaction system as well as other software designs.

The lead software engineer of the UVSIM simulator was Lixin Zhang from the University of Utah. I would like to thank Lixin for his help during initial UVSIM development.

Last, but definitely not least, I would like to thank Jennifer Song, all my friends, and my family for their continued support.

This research was funded in part by National Science Foundation Grant ACI-032497, in part by the Singapore-MIT Alliance, and in part by a grant provided by Silicon Graphics, Incorporated.

## Contents

| 1        | Intr                        | roduction                                  | 11 |

|----------|-----------------------------|--------------------------------------------|----|

| <b>2</b> | $\operatorname{Th}\epsilon$ | e Case for Unbounded Transactions          | 15 |

|          | 2.1                         | Atomicity in Parallel Systems              | 16 |

|          | 2.2                         | Problems with conventional locking         | 18 |

|          | 2.3                         | Transactions: a better atomicity primitive | 22 |

|          | 2.4                         | Overcoming hardware limitations            | 25 |

| 3        | Rel                         | ated Work                                  | 29 |

|          | 3.1                         | Non-blocking synchronization               | 30 |

|          | 3.2                         | Software transactional memory              | 32 |

|          | 3.3                         | Hardware transactional memory              | 33 |

| 4        | $\operatorname{Th}\epsilon$ | e UTM Design                               | 39 |

|          | 4.1                         | Design overview                            | 40 |

|          | 4.2                         | ISA modifications                          | 41 |

|          | 4.3                         | Transactional state in cache               | 44 |

|          | 4.4                         | Transactional state in main memory         | 47 |

|          | 4.5                         | Conflict detection                         | 52 |

|          | 4.6                         | Processor snapshot                         | 54 |

|          | 4.7                         | Nontransactional instructions              | 57 |

|          | 4.8                         | Context-switch support                     | 60 |

| 5 | Eva | uation                                  | 67  |

|---|-----|-----------------------------------------|-----|

|   | 5.1 | Evaluation environment                  | 68  |

|   | 5.2 | Overall performance                     | 70  |

|   | 5.3 | Transaction size and length             | 71  |

|   | 5.4 | Memory latency overhead                 | 74  |

|   | 5.5 | Effect of pipeline modifications        | 75  |

|   | 5.6 | Parallel transactional program behavior | 77  |

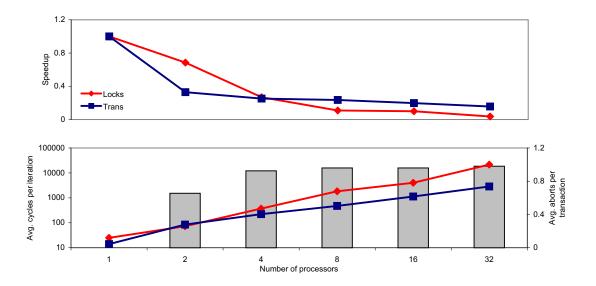

|   |     | 5.6.1 The NodePush microbenchmark       | 77  |

|   |     | 5.6.2 The Counter microbenchmark        | 78  |

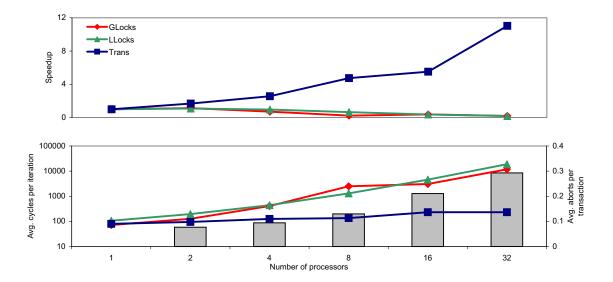

|   |     | 5.6.3 The BinaryTree microbenchmark     | 80  |

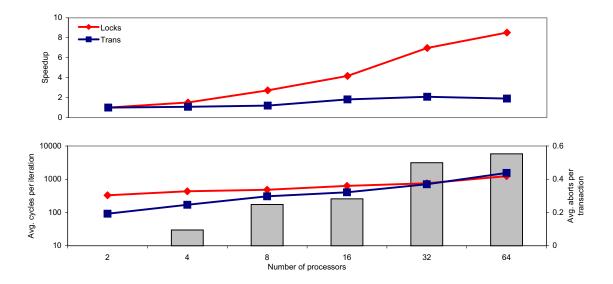

|   |     | 5.6.4 The LinkedList microbenchmark     | 82  |

| 6 | Des | gn Alternatives                         | 85  |

|   | 6.1 | Integrated hardware-software approach   | 86  |

|   | 6.2 | Linear overflow data structure          | 91  |

|   | 6.3 | Software register snapshot              | 93  |

|   | 6.4 | Nested independent transactions         | 96  |

| 7 | Con | clusions 1                              | 103 |

# List of Figures

| 2-1 | The node_push code example                                 | 16 |

|-----|------------------------------------------------------------|----|

| 2-2 | A potential problem running node_push in parallel          | 17 |

| 2-3 | node_push with global locking                              | 18 |

| 2-4 | node_push with incorrect fine-grained locking              | 19 |

| 2-5 | A deadlock example                                         | 19 |

| 2-6 | node_push with correct fine-grained locking                | 20 |

| 2-7 | node_push with transactions                                | 23 |

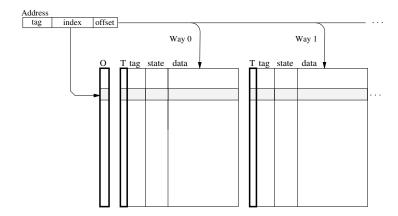

| 4-1 | Speculative transactional storage in cache                 | 44 |

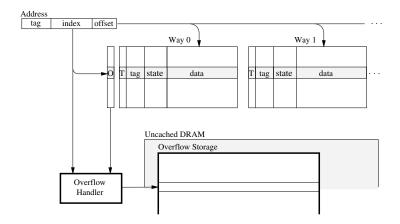

| 4-2 | Speculative transactional storage in cache and main memory | 48 |

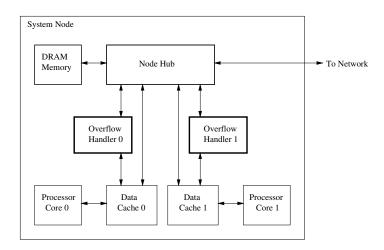

| 4-3 | Overflow handler interface to cache and memory             | 49 |

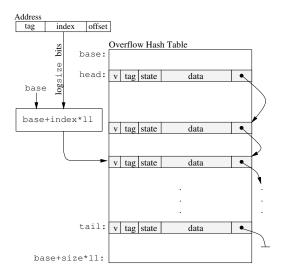

| 4-4 | Overflow hash table function and data structure            | 50 |

| 4-5 | Architectural register snapshot mechanism                  | 55 |

| 4-6 | A nontransactional logging example                         | 58 |

| 4-7 | Context-switch mechanism                                   | 61 |

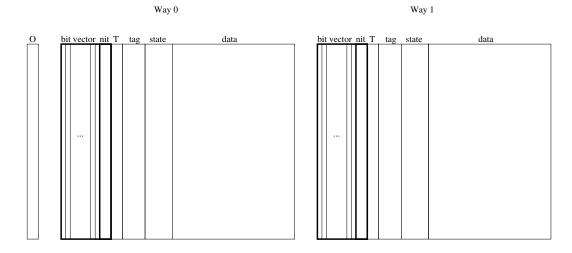

| 4-8 | Cache modifications for optimized context-switches         | 65 |

| 5-1 | UVSIM simulation parameters                                | 68 |

| 5-2 | SPECjvm98 performance                                      | 71 |

| 5-3 | SPECjvm98 transaction size and length distribution         | 72 |

| 5-4 | SPECjvm98 transaction overflow statistics                  | 72 |

| 5-5 | SPECjvm98 memory access latency                            | 74 |

| 5-6 | Processor modification effects on SPECjvm98 performance    | 76 |

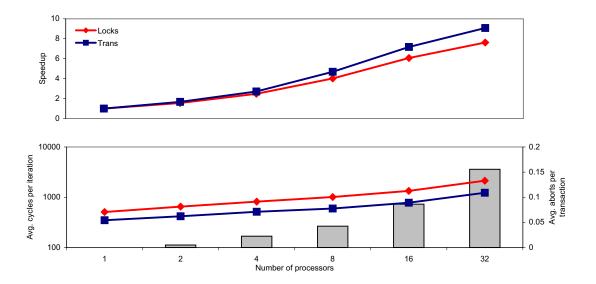

| 5-7 | NodePush microbenchmark performance                        | 78 |

| 5-8  | Counter microbenchmark performance                        | 79 |

|------|-----------------------------------------------------------|----|

| 5-9  | BinaryTree microbenchmark performance                     | 81 |

| 5-10 | LinkedList microbenchmark performance                     | 83 |

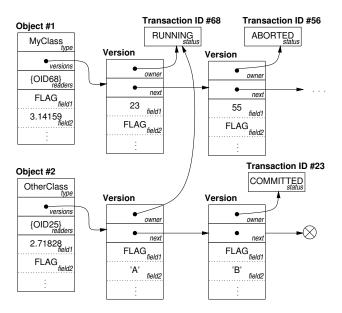

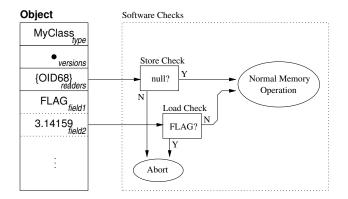

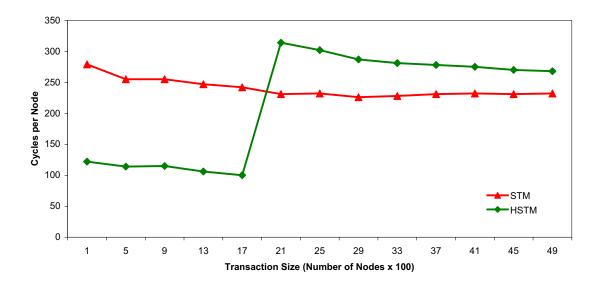

| 6-1  | STM object structure                                      | 87 |

| 6-2  | Additional checks performed on HTM operations             | 89 |

| 6-3  | HSTM performance for various transaction sizes            | 90 |

| 6-4  | SPECjvm98 performance with linear overflow data structure | 92 |

| 6-5  | Cache modifications for NIT implementation                | 97 |

## Chapter 1

## Introduction

Locks are conventionally used to achieve atomicity in parallel systems. Locks, however, have a host of problems such as deadlock. These problems introduce subtle correctness issues into parallel programs. Therefore, programming with locks is not an easy task.

Transactional memory [22, 23, 26, 27] has been proposed as an alternative means of achieving atomicity by presenting a more intuitive atomicity primitive to the programmer. Using transactional memory, the problems associated with conventional locks can be avoided. Transactional memory allows programs to read and modify many distinct memory locations atomically as a single operation, much as a database transaction [13, 14] can atomically modify many records on disk. The programmer simply specifies the scope of the transaction and the underlying system ensures it is executed atomically.

Although the implementation of transactional memory is undoubtedly more complex than conventional locks, previous work shows that hardware support can minimize the performance and implementation overhead [22,23]. Unfortunately, previous hardware transactional memory systems restrict the size of a transaction to that of a hardware buffer such as a cache. Although this limitation simplifies the hardware implementation, it also exposes the transaction size limit to the programmer. Exposing such an implementation parameter greatly restricts the ability to use transactional memory in practice.

In this thesis, I propose a hardware transactional memory system that does not have a hard limit on transaction size. This system, called UTM (unbounded transactional memory), uses the cache and cache-coherency protocol to store transactional state and detect conflicting transactions in much the same way as previous hardware designs. Unlike previous schemes, however, UTM allows transactional state to overflow from the cache into main memory. Therefore, UTM transactions are not limited to the size of a specialized hardware buffer such as the cache.

UTM can be implemented in a modern microprocessor with few changes to existing hardware while still achieving better performance than conventional locking techniques. To accommodate UTM, only the cache and processor require modification. Therefore, UTM is a practical design that can be implemented in today's microprocessors with low risk. Further, the simple implementation does not entail a loss in performance. UTM was implemented in a detailed system simulator, and experimental results with the SPECjvm98 [51] benchmark suite show that UTM outperforms conventional locking in all cases.

UTM also provides many other features not found in previous transactional memory systems. The semantics are simple and support transaction nesting and immediate aborts. The semantics are provided using a hardware snapshot of the processor architectural state. UTM also permits logging or debugging code within a transaction through nontransactional instruction blocks. Lastly, context-switches are supported during transaction execution without aborting the running transaction.

In the following chapters, I describe the UTM design in detail and present qualitative and quantitative evaluations of the design. In Chapter 2, I discuss the case for UTM. I argue that unbounded hardware transactions are necessary for a practical and efficient system. In Chapter 3, I present previous transactional memory designs and other related work. I contend that although previous designs have many useful characteristics, they all lack features that prevent them from being useful in practice. In Chapter 4, I describe the UTM design in detail and discuss the reasons behind the design decisions. I show that UTM can indeed be implemented with only minor hardware modifications. In Chapter 5, I provide a quantitative evaluation of UTM

based on simulation results. I show that UTM has low performance overhead and, in fact, performs better than conventional locking in most cases. In Chapter 6, I discuss some design alternatives and their design trade-offs. I argue that UTM strikes a good balance between hardware complexity and programming ease. In Chapter 7, I discuss UTM's limitations but argue that they do not prevent UTM from being useful in practice.

## Chapter 2

## The Case for Unbounded

## **Transactions**

Locks are conventionally used to achieve atomicity in parallel systems. Conventional locks, however, have many fundamental problems. Locks are hard to use and have high performance overhead. Further, locks are inherently conservative and blocking. Transactions are designed to solve the locking problems. Transactions are easy to use and potentially have extremely low overhead. Further, transactions are also optimistic and non-blocking. Unfortunately, previous hardware transaction designs impose a limitation on transaction size and length. This limit restricts the practical use of hardware transactions.

In this chapter, I argue that unbounded transactions are necessary in a practical transactional memory system. In Section 2.1, I describe how conventional locks are used. In Section 2.2, I discuss the fundamental problems associated with locks. In Section 2.3, I describe the transaction concept and its benefits over conventional locks. In Section 2.4, I introduce the notion of an unbounded transaction that does not suffer from size or length limitations.

```

if (Flow[i] > Flow[j]) {

Flow[i] = Flow[i] - X;

Flow[j] = Flow[j] + X; }

```

**Figure 2-1:** The node\_push code example. Flow X is being pushed from node i to node j only if node i has more flow than node j.

### 2.1 Atomicity in Parallel Systems

Shared memory multiprocessor architectures present a single unified address space to each processor. If one processor makes a change to main memory, the change is immediately visible to all other processors. Therefore, atomicity is often required for correct parallel program execution. Conventionally, this atomicity has been achieved through mutual exclusion locks. In this section, I describe the shared-memory architecture and how conventional locks are used.

Although shared-memory architectures present a single address space to all processors, the memory is usually physically distributed across the system. Each processor is able to access any part of it through a single address space. The system hardware is responsible for presenting this abstraction to each processor. Processors communicate implicitly through normal load and store operations on memory. Therefore, a load operation may result in fetching data from the memory or even the cache of a remote node. Data communication and cache-coherency is performed either over a common bus [11,41] or over a network using directories [1,35]. This mechanism is abstracted away from the programmer, however, which makes the shared-memory environment natural and well suited for many applications.

In shared memory programs, the ability to perform several memory operations atomically is often required for correct program execution. Consider, for example, the  $node\_push$  code given in Figure 2-1 which pushes flow X from node i to node j only if node i has more flow than node j. Similar code can be found in graph algorithms such as the parallel push-relabel maximum-flow algorithm [3, 10]. The code in Figure 2-1 operates as expected when run on a single processor. Running the code on several processors, however, may give unexpected results.

Initial values: Flow[0]=5, Flow[1]=4

| Processor 0                                        | Processor 1                                                                                |

|----------------------------------------------------|--------------------------------------------------------------------------------------------|

| if (Flow[0] > Flow[1]) {                           | <pre>if (Flow[0] &gt; Flow[1]) {   Flow[0] = Flow[0] - 2;   Flow[1] = Flow[1] + 2; }</pre> |

| Flow[0] = Flow[0] - 2;<br>Flow[1] = Flow[1] + 2; } | riow[i] - riow[i] · 2, }                                                                   |

Final values: Flow[0]=1, Flow[1]=8

Expected values: Flow[0]=3, Flow[1]=6

Figure 2-2: A potential problem running node\_push in parallel. The node\_push code is run on two processors. The order in which instructions are executed is shown with time running down.

Consider the possible parallel execution of node\_push shown in Figure 2-2. The result of that execution is not possible in a single-processor since the if condition would fail on the second push attempt. To get the expected result in parallel, it is necessary to execute the entire operation as one atomic operation. Although not illustrated in the example, it also is necessary to ensure that the increment and decrement occur as one atomic operation. For example, the statement [Flow[j] = Flow[j] + X] is usually translated into at least 3 instructions (load, increment, and store) in a RISC ISA. Therefore, it is necessary to ensure that these three instructions occur atomically as well.

Traditionally, mutual exclusion locks have been used to solve this problem. A lock is a memory location that, by convention, protects a block of code that needs to be run atomically. Once a processor obtains the lock, that processor can execute the atomic block. All other processors wanting to execute that code must wait until the lock is released. The processor holding the lock must release it once it is done executing the atomic block. This entire mechanism is a convention that is maintained by software alone. The hardware only provides the necessary mechanisms to acquire, release, and check the status of any lock.

```

Lock(globalL);

if (Flow[i] > Flow[j]) {

Flow[i] = Flow[i] - X;

Flow[j] = Flow[j] + X; }

UnLock(globalL);

```

Figure 2-3: node\_push with global locking. A single global lock globalL is used to ensure atomicity.

### 2.2 Problems with conventional locking

Although locks can be used to achieve atomicity, they inherently have three unavoidable problems. Firstly, locks are hard to use for programmers because they can lead to undesirable results such as deadlock when used incorrectly. Further, even when locks are used correctly, the addition of locks to serial code generally results in significant performance overhead. Lastly, locks are not well suited to exploit the concurrency in some applications since locks are conservative and blocking. In this section, I describe these problems in detail.

#### Locks are hard to use

The easiest way to achieve atomicity is with coarse-grained locks. Coarse-grained locking can be done in the node\_push example by using a single global lock as shown in Figure 2-3. A single global lock protects the atomic block so that only one processor can run that block at any given time. Using coarse-grained locks, however, can result in poor performance since it can hide the available concurrency. For example, in node\_push, theoretically, two processors can execute the same code block at the same time as long as they are operating on different nodes. A single global lock prevents such concurrency.

Since a fundamental goal of running an application in parallel is to increase performance, coarse-grained locking is often avoided in favor of fine-grained locking, which enhances concurrency. Unfortunately, fine-grained locking requires more locks, and the relationship between the locks can become complicated. For this reason, deadlock can become a problem once there is more than one lock. Deadlock is the situation

```

Lock(L[i]);

Lock(L[j]);

if (Flow[i] > Flow[j]) {

Flow[i] = Flow[i] - X;

Flow[j] = Flow[j] + X; }

UnLock(L[i]);

UnLock(L[i]);

```

Figure 2-4: node\_push with incorrect fine-grained locking. A lock for each node is acquired before the atomic block and released after the atomic block.

| Processor 0                                    | Processor 1                       |

|------------------------------------------------|-----------------------------------|

| Lock(L[0])  Lock(L[1])  Waiting on Processor 1 | Lock(L[1])                        |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,        | Lock(L[0]) Waiting on Processor 0 |

**Figure 2-5:** A deadlock example. The node\_push code with incorrect locking is run on two processors. The order in which instructions are executed is shown with time running down. No progress is made since processor 0 is waiting on processor 1 and processor 1 is waiting on processor 0.

where two processors cease to make progress since each processor waits on the other to release a lock. Unfortunately, deadlock can be hard to avoid.

To illustrate fine-grained locking and the problem of deadlock, consider using fine-grained locks in the node\_push example. Since it is desirable for processors to operate on different nodes concurrently, it is natural to associate a lock with each node. Since node\_push operates on two nodes within the atomic region, it is necessary to acquire the locks for both nodes. Figure 2-4 shows a naive incorrect implementation for node\_push. A lock for each node is acquired before the atomic block and released after the atomic block. Although, in most cases the naive implementation works correctly, in some cases it deadlocks. As shown in Figure 2-5, it is possible for two processors to wait on each other indefinitely.

It is possible to avoid deadlock by simply ordering the lock acquisition as shown

```

if (i<j) {

a = i;

b = j;

} else {

a = j;

b = i; }

Lock(L[a]);

Lock(L[b]);

if (Flow[i] > Flow[j]) {

Flow[i] = Flow[i] - X;

Flow[j] = Flow[j] + X; }

UnLock(L[b]);

UnLock(L[a]);

```

**Figure 2-6:** node\_push with correct fine-grained locking. Lock are acquired in order to avoid deadlock.

in Figure 2-6. Since locks are acquired in order, the deadlock situation from Figure 2-5 is not possible. It should be evident that deadlock avoidance adds significant complexity, however, even in such a simple example. In more complicated situations, reasoning about deadlock becomes even more error prone, leading to buggy programs.

When using locks, there is a tradeoff between programming ease and concurrency. It is always possible to use conservative coarse-grained locks but doing so greatly limits the concurrency and can result in poor performance. To achieve better performance, programmers can use fine-grained locking. Unfortunately, because of deadlock, programming complexity only increases as more fine-grained locking is used.

### Locks have high overhead

Although fine-grained locking can increase concurrency, locks still add a significant performance overhead as it takes time to perform deadlock prevention and lock acquisition and release. As shown in Figure 2-6, even simple lock ordering adds a significant overhead to a small transaction. There are simply many more instructions to run. There may even be an additional unpredictable branch if the ISA does not have instructions such as minimum, maximum, or conditional-move. Further, lock ac-

quisition is conventionally done using load-linked/store-conditional [25] instructions or atomic read-modify-write [30] instructions such as test-and-set, fetch-and-add, or compare-and-swap. These instructions can incur higher performance overhead compared to normal memory instructions.

In additional to performance overhead, using locks adds a significant space overhead as well. Locks are memory locations. In our example, each node in the graph requires one lock. For a large graph, this space overhead can be quite large. Further, although in theory a lock only needs to be one bit in size, in practice every lock must reside on a different cache line. Giving each lock its own cache line prevents problems such as false-sharing [17, sec. 8.3] that are caused by the underlying cache-coherency mechanism used to obtain exclusive access to lock variables. Therefore, the space overhead incurred by locks is often significant and cannot be ignored.

#### Locks are conservative

Conventional locking is inherently conservative. A lock may be obtained and released without any attempts by other processors to obtain that lock. Such a situation is common in highly parallel applications where contention is usually low. Therefore, locking is not necessary for the most part, but is nevertheless required to ensure correctness in the few cases where a conflict does occur. For example, in node\_push the overhead of lock reordering and lock acquisition/release is incurred even if all other processors are accessing different nodes, which is likely in a large graph. Thus, locks are always used but only rarely needed. Further, locks must be acquired even if the if condition fails and no push is necessary. Therefore, even highly optimized fine-grained locks can lead to suboptimal performance and unnecessarily high resource overhead.

### Locks are blocking

Conventional locking does not have a strong forward-progress guarantee. If a thread holding a lock is suspended for any reason, all other threads waiting for the lock do not

make any progress. Threads can be suspended for many reasons in modern systems since context-switches occur regularly. For example, if a thread running a small atomic region is switched out by the operating system, all other threads contending for the lock are left idle waiting for the thread holding the lock to be switched back in. The blocking nature of locks causes poor and unpredictable performance.

## 2.3 Transactions: a better atomicity primitive

The transaction is a primitive designed to provide atomicity without the problems associated with locks. Transactions are easier to use and potentially have much lower performance overhead. Further, transactions can exploit the concurrency often hidden by locks since transactions are optimistic and non-blocking. In this section, I describe the transaction concept in more detail.

Locking is used because it is the only way to achieve atomicity in current parallel systems. The programmer does not need locks per se. Atomicity suffices. Locks can achieve atomicity but they also distract the programmer from his true needs. Ideally, the underlying system provides an atomicity primitive that is deadlock free and able to exploit available concurrency while abstracting away the implementation details. The transaction is such a primitive.

A transaction, as in a database system, is an atomic block of code that can either commit or abort. If a transaction commits, the underlying system ensures that all memory operations within the transaction appear atomic with respect to other transactions or memory operations in the global memory system. If the underlying system cannot run the transaction atomically for any reason, it is aborted and the transaction appears to have not run at all.

Conceptually, the code within a transaction is run speculatively until the end of the transaction. If the speculative execution does not conflict with another transaction or memory operation, the speculative changes are committed, thereby committing the transaction. On the other hand, if a conflict occurs before the end of the transaction, the speculative changes are rolled back to the beginning of the transaction and it

```

xBEGIN;

if (Flow[i] > Flow[j]) {

Flow[i] = Flow[i] - X;

Flow[j] = Flow[j] + X; }

xEND;

```

Figure 2-7: node\_push with transactions. The xBEGIN and xEND commands mark the start and the end of the transaction respectively. The underlying system ensures that the block is run atomically.

appears as if the transaction was not run at all. In the event that two transactions conflict while running speculatively, only one needs to be aborted and the other can be allowed to continue. Which transaction to abort is an implementation specific policy. In theory, both transactions can be allowed to continue as long as the underlying system ensures that each transaction always sees a consistent view of memory. For example, one can create multiple versions of the modified data as in multi-version database systems [4,52]. The amount of bookkeeping necessary for such a system, however, often precludes an efficient hardware implementation.

### Transactions are easy to use

Transactions are much easier to use than locks since the programmer need not worry about issues such as deadlock. As shown in Figure 2-7, using transactions is straightforward. The programmer simply wraps each atomic region in a transaction and the underlying system ensures that it is executed atomically.

#### Transactions can have low overhead

It is possible to implement the transaction primitive in hardware with negligible performance overhead. Herlihy and Moss [22,23] and Knight [26,27] propose transactional memory implementations that use the cache and cache-coherency mechanisms of modern parallel systems to provide the transaction primitive with virtually no overhead. These hardware systems use the processor cache to store the transaction's speculative state and use the cache-coherency protocol to detect conflicts. The specu-

lative state in the cache can be committed or aborted by simply flash clearing certain bits in the modified cache. Therefore, there is essentially no performance loss. More details about these systems can be found in Chapter 3. The previous work on hardware transaction systems provides evidence that transactions can be achieved with low overhead.

#### Transactions are optimistic

The speculative nature of transactions implies that transactions are inherently optimistic. Two transactions can run concurrently as long as they do not access the same memory location in a conflicting manner. The two transactions can even be separate instances of the same atomic region that would have been protected by a single lock conventionally. With a single lock, only one processor can execute the atomic region at any given time. The other processors are forced to wait even if no conflict occurs. With transactions, on the other hand, many processors may execute the same atomic region simultaneously in the absence of conflicts. Each processor simply executes speculatively independent of the other processors. If no conflict occurs, every processor can commit its transaction independently as well. For example, in node\_push, two transactions can even operate concurrently on the same pair of nodes if both if statements fail since neither transaction is writing any data.

### Transactions are non-blocking

A transaction guarantees forward-progress if all conflicting transactions suspend execution for any reason. The running transaction simply proceeds by aborting all conflicting suspended transactions. Therefore, unpredictable interruptions such as context-switches and exceptions cannot affect other threads. The non-blocking nature of transactions thus results in lower runtime and more predictable performance.

## 2.4 Overcoming hardware limitations

Although previous hardware transactional memory designs have low overhead, they also impose a restriction on the size and length of transactions. These limitations restrict the use of these systems in practice. In this section, I first describe these limitations in more detail. Then I describe the notion of an unbounded transaction that does not suffer from these limitations.

The designers of previous hardware transaction designs assume that transactions are generally small and short. Therefore, they claim it is acceptable to imposed a size and length limitation on transactions. For clarity, transaction size refers to the number of distinct memory locations touched by a transaction. Transaction length refers to the time it takes to run a transaction. Systems with size or length limitations are referred to as bounded. Systems without these limitations are referred to as unbounded. In previous bounded systems, transactions that are too big or too long are simply aborted.

The designs by Herlihy and Moss [22,23] and Knight [26,27] expose a strict transaction size limitation since they only use a hardware buffer to store the running transaction's speculative state. When the buffer is full, the transaction is aborted. Although such an implementation can lead to low overhead, it also imposes an awkward restriction. If a transaction aborts because of a space limitation, that transaction can never run successfully on the system.

The length limitation imposed by previous bounded systems is not a hard limit like the cache capacity. Instead, the length limitation arises from the fact that previous hardware systems do not support context-switches during a transaction. When a context-switch is performed, the running transaction is simply aborted. Since modern multithreaded systems have context-switches at regular intervals, such a restriction effectively limits the length of the transaction. Like the size limitation, this restriction is awkward. If a transaction aborts because it is longer than the process time slice, that transaction can never run successfully on the system.

Although the assumption that most transactions are small and short may still

hold in common applications, the bounded approach leads to a impractical system. In the remainder of this section, I discus in more detail the reasons why unbounded transactions are necessary.

#### The need for unbounded transactions

The main goal of transactions is to simplify concurrent programming. ¿From the point of view of a programming language or compiler, however, bounded transactions lead to complications that reduce their advantages over locking. For transactions to be truly useful in a systems setting, they must be unbounded.

The transactional size limitation exposes an awkward architectural parameter in the instruction-set architecture (ISA). Ideally, such a limitation should be an implementation parameter such as memory or cache size. Implementation parameters can vary from machine to machine of the same type. Unfortunately, the size limitation must be exposed as an architectural parameter since machines with different limitations cannot run the same programs. For example, an application binary that contains a transaction that touches 180 bytes will not run correctly on a system with a size limitation of 160 bytes. It will run correctly, however, on a system with a size limitation of 200 bytes. Often the cache, whose size is an implementation parameter, is used to store transactional data. Different revisions of the same processor may have different cache sizes and thus behave drastically differently when running the same transactional binary.

Even if the size limitation is exposed as an architectural parameter, many unsolved problems remain. For example, what should that limitation be? Should the system support transactions that touch 10 bytes? 100? 1000? And, how is this bound enforced? Suppose that the system supports transactions of 1000 bytes or less. What should the compiler or programmer do with a program containing larger transactions?

It is even unclear how the programmer or the compiler would find the size of the transaction. For example, modern programming languages such as C [28] seldom expose memory references to the programmer. In C, without the volatile keyword the programmer has no way of knowing whether a given memory reference actually causes

a memory operation or if the compiler optimizes it away. Since the programmer cannot find the size of the transaction, one might argue that perhaps the compiler can. Unfortunately, that task is just as difficult for the compiler. General programming practice allows the calling of subroutines without knowing how many memory references they make. Also, often the number of memory references is only determined at runtime. Of course, it may be possible for the compiler to expose the number of memory references to the calling function. Moreover, it may be possible for the compiler to perform conservative analyses and forbid practices such as using loops within transactions to restrict the possibility of dynamically sized transactions. Perhaps we can force that transactions are only accessible to the programmer through hand-coded runtime libraries. Although all of these options are technically viable, they prevent transactional memory from being a general system-building tool.

The transaction length limitation is equally difficult to deal with in a real system. Should the minimum process time slice be an architectural parameter? What does the operating system do if a transaction cannot finish within the process time slice? How does the programmer or the compiler know how long a transaction will run for?

Because none of these questions has a good answer, I contend that the size and length limitations of the underlying system should be viewed as implementation parameters which can vary without affecting the portability of binaries. Code should not need to be rewritten or recompiled to deal with a different internal hardware limit. Internal limitations may be visible as a matter of performance like the cache size but the same application binary should always run correctly on different revisions of the same machine. Therefore, from a systems perspective, unbounded transactions are essential to the design of a practical transactional memory system. Truly unbounded transactions are, of course, never possible since no system has unlimited resources. The visible limits should be sufficiently large, however, that programmers never encounter it. For example, there is technically a limit to the amount of virtual memory in a system, but it is sufficiently large that the programmer need not worry about it.

## Chapter 3

## Related Work

The concept of optimistic transactions was first described in the database context by Gray [13] and Reuter [14] and Kung and Robinson [32]. Since then, the concept has been proposed for normal parallel programs, not just those related to databases. The general goal is to make parallel programming easier and to exploit concurrency often hidden by conventional locks. Three general approaches have been explored: the non-blocking approach, the software transaction approach, and the hardware transaction approach. The non-blocking approach does not require hardware changes and has a forward-progress guarantee. The software transaction approach also does not require hardware changes since the atomicity primitive is provided through programming languages, compilers, and libraries. The hardware transaction approach provides the atomicity primitive through hardware and ISA modifications.

In this chapter, I describe related work in these three areas. Unfortunately, certain aspects of all previous systems restrict their use in practice. In Section 3.1, I describe non-blocking synchronization. I argue that non-blocking synchronization adds too much programming complexity. In Section 3.2, I explore previous software transactional memory designs. I argue that software designs have impractically high performance overhead. In Section 3.3, I describe previous hardware transactional memory designs. I argue that although hardware designs have low performance overhead, they all have restrictions such as size or length limitations that restrict their practical use.

### 3.1 Non-blocking synchronization

Non-blocking synchronization is a software technique that provides atomicity without mutual exclusion locks. Since locks are not used, their associated problems are also avoided. For example, non-blocking synchronization is optimistic and deadlock free. In addition, since it is a software technique, hardware changes are not necessary. Standard instructions such as compare-and-swap or load-linked/store-conditional are sufficient. Further, non-blocking synchronization has a strong forward-progress guarantee. Unfortunately, non-blocking synchronization increases program complexity and makes parallel programming more difficult. Several varieties of non-blocking synchronization have been proposed including lock-free [33], wait-free [18], and obstruction-free [20] synchronization. In this section, I describe these non-blocking techniques in more detail and discuss their impact on programming complexity.

Lock-free synchronization was first explored by Lamport [33] and later formalized by Herlihy [19]. A concurrent object is lock-free if *some* concurrent thread is guaranteed to complete an operation in a finite amount of time. A systematic methodology can transform any concurrent object into a lock-free object [19]. First, a copy of the concurrent object is made and used for modifications. The modified copy is then switched back into the concurrent data structure by changing a pointer with a load-linked/store-conditional operation. If the store-conditional fails, the operation is retried since another thread must have changed the data structure after the copy was made. The lock-free technique guarantees forward-progress since at least one of the threads attempting to modify the concurrent object will succeed.

Wait-free synchronization was later proposed by Herlihy [18] to have an even stronger progress guarantee. A concurrent object is wait-free if every concurrent thread is guaranteed to complete an operation in a finite amount of time. To achieve this stronger progress guarantee, wait-free objects are significantly more complex than lock-free objects. A methodology similar to that for lock-free objects can be used to transform any concurrent object into a wait-free object [19]. The thread also starts by making a copy to which modifications are made. In addition to making the copy,

the thread also globally announces its intended modification. Each time a thread attempts to make any modification, it also performs any outstanding modifications announced by other processors. As in lock-free synchronization, at least one of the concurrent threads will succeed. The successful thread, however, has also made the modifications for unsuccessful threads. Therefore, all the threads will be successful within a finite amount of time.

Both lock-free and wait-free objects are optimistic and have attractive progress guarantees. Therefore, the techniques exploit much of the concurrency that conventional locks tend to hide. Herlihy shows that lock-free and wait-free synchronization can outperform spin-locks in some situations.

Herlihy suggests that the systematic transformation of any object into a lock-free or wait-free object can be done automatically by the compiler. Therefore, in theory, the programmer need not deal with the added complexity. In practice, however, lock-free and wait-free techniques are rarely used. A possible explanation for the lack of acceptance is that implementing lock-free and wait-free objects is not as straight forward as Herlihy first imagined. If the process cannot be automated, the added programming complexity is clearly a significant deterrent. Even the simple wait-free dequeue operation Herlihy presents in [19] is difficult to understand and significantly more complicated than using conventional locks. Therefore, although lock-free and wait-free synchronization have many of the performance benefits of transactions, they do not address the programmability problem since they can make parallel programming even more difficult.

The programmability problem was, in fact, recognized by Herlihy who recently proposed another type of non-blocking synchronization: obstruction-free objects [20]. A concurrent object is obstruction-free if an isolated thread is guaranteed to complete an operation in a finite amount of time. An isolated thread is a thread running without any conflicts from other threads. Although the progress guarantee is much weaker than that of lock-free or wait-free objects, Herlihy shows that obstruction-free objects share many of their advantages while being easier to program. Unfortunately, there is no systematic transformation that can be performed by the compiler. Herlihy

shows the obstruction-free technique by example with a few simple data structures. Although the technique is easier to program than lock-free or wait-free objects, there is still a significant complexity overhead.

Non-blocking synchronization is able to overcome many of the problems of associated with conventional locks. Despite its many advantages, however, non-blocking techniques have not been widely adopted by the parallel programming community. The reason for its lack of popularity lies in its inherent complexity. Instead of making parallel programming easier, non-blocking synchronization actually makes it more difficult.

## 3.2 Software transactional memory

Several software transaction systems have been proposed. Software designs have the advantage that they require no change to the hardware and generally do not impose transaction size or length limitations. Software systems are generally implemented by inserting additional code by modifying the compiler. Therefore, they can also take advantage of compiler analysis and optimization. Unfortunately, software transactions generally have high performance overhead. In this section, I describe previous work on software transactional memory and the associated performance overheads.

The first design for software transactional memory was proposed by Shavit and Touitou [47]. Their system requires that all input and output locations touched by a transaction be known in advance. This restriction limits its application. Further, it performs at least 10 additional loads and 4 additional stores per memory location accessed as part of a transaction.

Rudys and Wallach [45] proposed a copy-based transaction system to allow roll-back of hostile code blocks. On one processor, they show an order of magnitude slowdown for field and array accesses and a 6-23x slowdown on their benchmarks.

Herlihy, Luchango, Moss, and Scherer's scheme [21] allows transactions to touch a dynamic set of memory locations. The user needs to explicitly open every object before it can be used in a transaction. This implementation is based on object copying.

and thus has poor performance for large objects and arrays. They present a list insertion benchmark on one processor that shows a 9x slowdown over a locking scheme.

Harris and Fraser built a software transaction system on a word-oriented transactional memory abstraction [16]. Their scheme effectively makes a speculative copy of each word in the transaction and operates on that copy during the transaction. Their scheme only copies the data being accessed at a word granularity thus avoiding the problems with large objects. With this technique, they are able to decrease the overhead significantly. Single-processor overhead, however, is still 2x over locks for some specially-coded microbenchmarks.

Unlike non-blocking synchronization, software transactional memory is implemented in the compiler. Therefore, the synchronization details are abstracted away from the programming making software transactions easy to use.

Unfortunately, all of these software designs have high performance overhead. The fastest system is still 2x slower than conventional locks under ideal situations. The high overhead is not surprising since all the bookkeeping is done using normal software techniques. The large amount of bookkeeping simply precludes an efficient implementation.

All of these software designs generally have more reasonable performance overheads when running on many processors. With a lot of processors, and the appropriate application, the optimistic nature of transactions can overcome the high overhead. Typically the number of processors required for acceptable performance is much more than in modern small SMP systems. Thus, software transactional memory is impractical for general use in real systems.

### 3.3 Hardware transactional memory

Hardware can be used to accelerate transactional bookkeeping. The technique has been explored in many different contexts. Hardware transactional memory was first proposed as a cache and cache-coherency mechanism to facilitate lock-free synchronization. A similar technique was independently studied as part of work on thread-

level speculation and speculative locks. Recently, there has also been a transactional memory system developed at Stanford University. Unfortunately, all of these systems impose limitations that restrict their practical use. In this section, I describe in more detail these hardware systems, their advantages, and their disadvantages.

Hardware transactional memory was first proposed by Herlihy and Moss [22, 23] and Knight [26, 27]. Herlihy and Moss coined the term transactional memory in the context of lock-free synchronization. I will call these systems HTM (hardware transactional memory). HTM exposes the transaction primitive in the ISA and uses a hardware buffer such as a cache to store speculative data. It also uses the cache-coherency mechanism to detect conflicting transactions. By using the cache and cache-coherency mechanisms, HTM provides the transaction primitive with low performance overhead.

In HTM, every transactional load or store operation brings the target memory block into the hardware buffer in the same way a block is brought into the cache. All speculative modifications are made to the data in the hardware buffer without affecting the previous consistent value in main memory. The hardware buffer is snooped on each incoming cache intervention message. If the incoming intervention hits a speculative line before the transaction commits, a conflicting access from another processor has been made. When this conflict is detected, the running transaction is aborted. Since the previous consistent values remain in main memory, the transaction can be aborted by simply invaliding all speculative lines in the hardware buffer. All future requests for these blocks will miss and require a load from main memory as in a silent drop. This mechanism effectively rolls back all speculative changes made by the transaction. When the transaction commits, all speculative lines in the hardware buffer are changed to non-speculative. This change effectively commits the speculative changes since non-speculative data is globally visible through the cachecoherency mechanism. Using the cache and cache-coherency mechanism this way allows execution of transactions with negligible performance overhead.

Although HTM was able to maintain low performance overhead, it imposed awkward size and length limitations on transactions as discussed in Chapter 2. These limitations prevent HTM from being useful in practice. The general cache-based approach is nevertheless valuable because of the low overhead. UTM uses this approach to achieve good common case performance.

The general notion of a transaction that HTM advocates is not shared by all previous hardware designs. Some designs have described the notion of a transaction as an extension to load-linked/store-conditional [25] and other complex atomic instructions. In fact, CISC machines such as the VAX have complex atomic instructions such as enqueue and dequeue [6]. These approaches limit the use of transactional memory to only a few specific applications.

Using the cache and cache-coherency protocol to store speculative data and detect conflicts was not only studied in the context of transactions. The notion was also explored independently in work on thread-level speculation (TLS). TLS has been investigated separately as part of the Multiscalar [49] project, the Hydra [42] project, the Stampede [53] project, and by Krishnan and Torrellas [29]. TLS executes interdependent threads speculatively, often out of order, but maintains the appearance of in-order execution at completion. The goal is to achieve better performance by speculating past false dependencies. For example, several iterations of a single-threaded loop can execute concurrently without losing the appearance of in-order execution in the absence of true inter-loop dependencies.

In TLS, there is one non-speculative thread and many speculative threads. All speculative threads can be aborted by the non-speculative thread but the non-speculative thread cannot be aborted. Speculative threads store speculative data in a hardware buffer such as a cache. The cache and cache-coherency mechanism detect conflicts and provide abort and rollback functionality as in HTM. Each speculative thread contains a timestamp. Once a non-speculative thread commits, the speculative thread with the smallest timestamp becomes non-speculative. If the speculative buffer requires overflow, TLS simply waits until the speculative thread becomes non-speculative. Then the hardware buffer can be flushed into main memory since the thread is no longer speculative.

The speculative nature of TLS is similar to that of transactions. Therefore, the

mechanisms necessary for TLS are similar to those used in HTM systems. TLS and transactions have different goals however. The goal of TLS is to increase performance and to automate code parallelization. On the other hand, the goal of transactions is to achieve atomicity without the problems associated with locks. TLS does not address the atomicity problem at all.

Another approach was proposed by Rajwar and Goodman called Speculative Lock Elision and Transactional Lock Removal (SLE and TLR) [43,44]. SLE/TLR is based on speculating past conventional locks. Similar schemes have also been developed by Martinez [36] and Rundberg [46]. SLE/TLR dynamically identifies locks and speculatively executes past them using the cache and cache-coherency mechanisms in a similar way as HTM. Since the programmer still uses locks as the underlying atomicity primitive, programs need not be recompiled to take advantage of SLE/TLR. In addition, if speculative execution cannot proceed for any reason (such as buffer overflow or context-switch), SLE/TLR falls back to locks to guarantee forward-progress. Although this technique has many of the performance advantages of a true transactional memory system, the codes must still obey a deadlock-free locking protocol. Thus they do not make programming easier.

Lastly, and most recently, a hardware design called Transactional memory Coherence and Consistency (TCC) [15] was developed at Stanford University. TCC takes a slightly different approach to transactions. TCC advocates that transactions be used everywhere. In TCC, the basic unit of work is a transaction. In contrast, in conventional systems, the basic unit is a memory operation. TCC proposes an entirely new cache-coherency and memory consistency model. In TCC, all transactions are executed speculatively in the cache but there is no conventional cache-coherency. Instead, at the end of each transaction, all speculative updates are broadcast to main memory and all other processors. Conflicts are detected by each processor upon receiving the broadcast.

TCC also overcomes any hardware size limitations with the broadcast mechanism. When a transaction requires more room than the cache, TCC simply starts broadcasting updates immediately as they are executed. The broadcasting processors does

not release the bus until the entire transaction completes. Since the processor holds the bus for the remainder of the transaction, it cannot be aborted.

Although TCC can overcome the hardware size limitation, it does not provide a mechanism that allows transactions to span context-switches. TCC does, however, provide a pseudo-overflow mechanism that allows non-atomic code blocks to broadcast updates before the end of the block. Pseudo-overflow can be used to prematurely end a non-atomic code block in the event of a context-switch or other exception. Pseudo-overflows, however, cannot be used in atomic transactions since it would expose inconsistent data. Therefore, like HTM, TCC must abort all atomic transactions on a context-switch.

The goal of TCC is to provide the transaction primitive while reducing the hard-ware complexity associated with conventional cache-coherency and memory consistency models. Since processors only broadcast on transaction commit, the TCC hard-ware need not support small low-latency messages required in conventional shared-memory systems. Unfortunately, although the hardware may be conceptually simpler, there are other hardware tradeoffs associated with the simplicity. For example, performing a global broadcast consumes more power than individual point-to-point transfers. Also, broadcasts are inherently not scalable. Thus TCC may only be practical for small SMP systems and not well suited for large scale multiprocessor machines.

In TLS, SLE/TLR, and TCC, transactions are not limited by the size of a hard-ware buffer. In all of these schemes, however, the size limitation is overcome by allowing the overflowing transaction to become non-speculative. In TLS, the oversized thread simply waits until its timestamp is the smallest in the system. In SLE/TLR, the system simply falls back to locks. In TCC, the oversized thread simply locks the broadcast bus until transaction commit. Although these approaches solve the problem, they effectively halt the rest of the system. Since the oversized transaction is non-speculative, it cannot be aborted. Therefore, all other speculative threads cannot commit until the overflowing transaction finishes. Such a mechanism can drastically decrease performance.

All previous hardware designs have one clear advantage over all software designs. Hardware is simply faster than software and thus the hardware systems have much lower performance overhead than software systems. Unfortunately, all previous hardware designs are limited in one way or another that prevents them from being truly practical systems.

# Chapter 4

# The UTM Design

UTM is a hardware transactional memory design where the transaction size is not bounded by a specialized hardware buffer such as a cache. As in previous hardware transactional memory systems, UTM uses the cache to store speculative state and uses the cache coherency protocol to detect conflicting transactions. Unlike previous hardware systems, UTM allows the speculative state to overflow from the cache into main memory, thereby allowing the transaction to grow beyond the size limitation of the cache. The clean semantics of UTM allow nested transaction support, nontransactional instructions, immediate aborts, a processor snapshot, and context-switching support; all features not found in previous hardware transactional systems.

In this chapter, I describe these UTM features in detail. In Sections 4.1 and 4.2, I give an overview of the design and present the transaction semantics. In Sections 4.3 and 4.4, I present how UTM stores transactional data in the cache and main memory with only minor hardware modifications. In Sections 4.5 and 4.6, I describe how UTM detects conflicts and rolls back register state when one is detected. In Section 4.7, I describe how UTM handles nontransactional instructions to support logging and debugging. In Section 4.8, I outline UTM's context-switch mechanism that leverages the overflow hardware.

## 4.1 Design overview

The goal in UTM is to achieve unbounded transaction with low performance and implementation overhead. This goal is reflected throughout the UTM design. UTM only requires changes to the cache and processor core. The network, cache-coherency protocol, and directory controllers are not modified. UTM uses the cache, as in previous designs, to achieve low performance overhead in the common case. UTM, however, is a significant extension of the previous hardware transaction designs. In this section, I present an overview of the UTM design focusing on its advances over previous hardware transaction designs.

Like the previous designs by Herlihy and Moss [22,23] and Knight [26,27], UTM primarily uses the cache to store speculative transactional data. Unlike their designs, UTM allows transactional data to overflow from the cache into a hash table in main memory. Therefore, UTM does not suffer from any size limitations. UTM augments the processor cache with less than 2 bits per cache line to keep track of transactional data and overflows.

At the ISA level, UTM differs from previous hardware designs since UTM supports transaction nesting and nontransactional instructions. UTM allows transactions to be nested by subsuming all nested transactions into the outermost transaction. This feature is achieved by simply adding a hardware counter to track the nesting depth. UTM also supports nontransactional memory instructions for debugging and logging during transaction execution.

The semantics of UTM also differ slightly from previous designs. UTM supports immediate aborts as opposed to a branch-on-abort type instruction as in the Herlihy and Moss design. UTM transactions are aborted immediately once a conflict is detected. The UTM hardware immediately rolls back all changes to the memory system and the processor's register state. There is a register snapshot mechanism that records the architectural state of the processor at the start of each transaction. The UTM snapshot mechanism uses much of the branch prediction hardware already in modern microprocessors. If the transaction commits, the snapshot is discarded.

Otherwise, when the transaction aborts, the snapshot is restored and the processor jumps immediately to the abort handler much like jumping to an exception handler.

UTM also supports context-switches during transaction execution. The running transaction is suspended on a context-switch. All transactional data in the cache is pushed out to a data structure in main memory. When the thread is switched back in, the transaction is resumed by repopulating the cache with the transactional data.

UTM is designed for an out-of-order superscalar processor in a multiprocessor environment where cache-coherency is handled using a directory-based protocol. The simulation of UTM presented in this thesis uses the MIPS R10000 [37, 55] processor and a non-uniform memory access (NUMA) network similar to the SGI Origin 2000/3000 [34] as the baseline. The design, however, is flexible enough to be adopted in any out-of-order superscalar processor that uses an invalidation-based cache-coherency protocol.

#### 4.2 ISA modifications

UTM provides the unbounded transaction primitive to the programmer through the processor ISA. UTM requires only minor changes to the ISA to accommodate easy integration into existing systems. The minor modifications, however, allow nested transactions, immediate aborts, and nontransactional instructions.

In this section, I describe the UTM semantics and the required ISA modifications. UTM adds the following basic instructions to the MIPS instruction set [38]:

**xBEGIN** pc: Marks the start of a transaction. The pc argument is the PC-relative address of the abort handler.

**xEND:** Marks the end of a transaction.

All instructions executed between the xBEGIN and xEND are considered part of the transaction. Semantically, the xBEGIN instruction can be viewed as a branch that jumps to the abort handler (pc) if the transaction cannot run atomically. Otherwise,

execution falls through to the first instruction in the transaction and always runs to the end of the transaction.

UTM also requires other additions to the processor ISA. This section only focuses on the most important instructions **xBEGIN** and **xEND**. The other instructions will be described as needed in other sections.

UTM supports properly nested transactions by subsuming all nested transactions into the outermost transaction. The xBEGIN and xEND instructions forming the inner nested transactions are effectively ignored. Only properly nested transactions are supported so an exception is signaled if improper nesting is detected.

Normal nontransactional loads and stores that occur outside transaction boundaries are treated as single-instruction transactions that cannot be aborted. Therefore, normal nontransactional memory operations always complete, even if doing so aborts a conflicting transaction.

UTM also supports nontransactional memory operations within a running transaction. Performing nontransactional operations within a transaction is necessary for tasks such as writing debugging information or logging transaction activity. Nontransactional semantics are described in Section 4.7.

## Design rationale

UTM semantics support transactional procedure calls naturally. If a procedure is called within a transaction, it is desirable treat the procedure as part of the transaction. The xBEGIN and xEND behavior support these semantics automatically since all instructions (even procedure calls) executed between the xBEGIN and xEND are treated as part of the transaction. Some previous hardware designs, such as Herlihy and Moss's system, used special transactional load and store instructions. As a result, two versions of every procedure must be compiler: a transactional version and a non-transactional version. The choice of which to use depends on whether the procedure is called from within a transaction. Since some codes such as legacy libraries cannot be recompiled, such a requirement complicates the integration of transactional memory into existing systems.

UTM nesting semantics also simplifies procedure calls from within a transaction. If transaction nesting was not supported, the programmer or the compiler needs to know if the called procedure actually uses transactions or not. Since this information is often difficult to obtain or even unavailable until runtime, UTM must support nested transactions. There are several ways to handle nested transactions however. The UTM approach of subsuming properly nested transactions is one of the simplest. Since UTM is not designed to provide general database-like transactions, simply subsuming nested transactions is sufficient.

The xBEGIN branch-like semantics are clean and easy to use. Some previous hardware designs, such as Herlihy and Moss's system, use branch-on-abort type instructions that are inserted throughout each transaction by the programmer. The branch-on-abort instruction branches to an abort handler address if the running transaction has been aborted. Such an approach, however, is difficult to use since it relies on the programmer to periodically check whether an abort has occurred. Since the memory system rolls back all transactional changes immediately after an abort, a transaction executing after the abort can read inconsistent data. Thus, the program can behave unexpectedly. For example, an infinite loop may occur before the program reaches a branch-on-abort instruction. UTM semantics avoid such situations altogether since the processor jumps directly to the abort handler immediately after the abort.

To provide sensible semantics for the immediate abort, UTM requires more hard-ware modifications. UTM needs to take a hardware snapshot of the processor's register state so that it can be restored on abort. The branch-on-abort approach does not require a hardware snapshot since the register state can be restored by software. Since the transaction can only enter the abort handler from one of a few branch-on-abort locations, the registers can only be in one of a few states after the abort. In theory, the abort handler software can then restore the registers.

Lastly, treating all normal nontransactional memory operations as small un-abortable transactions simplifies integration into existing systems. These semantics are natural and easy to understand since they are the same as the semantics of a normal nontransactional system. As in a normal system, memory operations not within a transaction

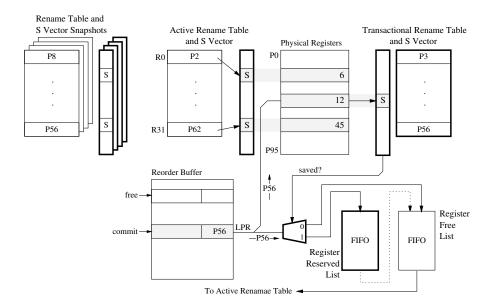

**Figure 4-1:** Speculative transactional storage in cache. The cache is the primary storage for speculative transactional data. Two ways of an N-way set-associative cache is shown. The T bit indicates if the cache line contains transactional data. The O bit indicates if the cache set has overflowed.

always affect the contents of main memory. All conflicting transactions are simply aborted. Therefore, transactional code can seamlessly operate alongside nontransactional code such as legacy libraries. Transactional applications can therefore be integrated into existing systems with low risk.

### 4.3 Transactional state in cache

UTM uses the cache as the primary storage space for speculative transactional data during transaction execution. As in previous designs, the cache allows for a straightforward implementation that has low performance overhead. In this section, I describe the necessary modifications to the cache.

While the cache holds the speculative data, the previous consistent data always remains in main memory. Speculative transactional updates are only performed on cache data. Speculative transactional data is only permitted to leave the cache after commit, thereby making all changes globally visible. Previous hardware transactional memory designs use the cache similarly.

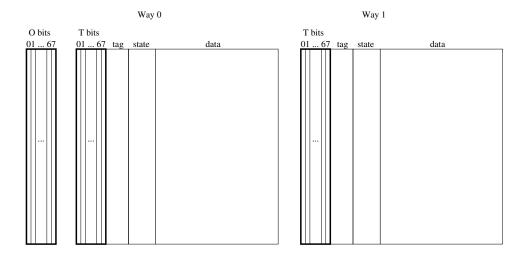

Storing transactional data in the cache requires only minor modifications as shown in Figure 4-1. UTM assumes a set-associative cache that is common in modern processors. One transaction (T) bit per cache line is added to indicate if the cache

line contains transactional data. One overflow (O) bit per cache set is added to indicate if the cache set has overflowed. These bits represent the transactional state in the cache. This section focuses on the transaction bits. Overflows are discussed in detail in Section 4.4.

At instruction decode, memory instructions are tagged as transactional if they are decoded between the outermost xBEGIN and xEND instructions. The nesting depth is tracked by an internal hardware counter which is initialized to zero when not in a transaction. The hardware counter is incremented and decremented on xBEGIN and xEND decode respectively. If the nesting level is greater than zero when a memory instruction is decoded, the instruction is tagged as transactional.

When a transactional memory operation hits in the cache, the target line is marked transactional by setting the T bit. If it misses in the cache, the target line is brought into the cache as in a normal memory operation, and then marked transactional. If a transactional store request hits a nontransactional modified cache line, the cache writes the old data back to main memory. The write-back is required to keep the non-speculative consistent value in memory so that speculative transactional changes can be rolled-back.

UTM stores transactional state in the outermost largest level of cache. In the MIPS R10000, transactional data is stored in L2 since it is the largest outermost cache. The L1 cache obeys the inclusion property so L1 data is always a subset of L2 data. UTM's transactional state obeys the inclusion property as well. Therefore, the L1 cache also contains transaction bits but they are simply a subset of those in the L2 cache.

The MIPS R10000 processor, like most speculative out-of-order processors, often speculatively issue memory load requests. For example, a load after an unresolved predicted branch is issued to the cache once the address is calculated. At that time, however, the load instruction is still speculative and thus may not even graduate from the processor pipeline. For example, if the branch is mispredicted, the load is flushed along with the rest of the instruction pipeline. Thus, some of the data brought into the cache may not be associated with any of the perceived graduated instructions.

Although the processor issues speculative load requests, UTM only stores transactional state for graduated instructions. Speculative loads cannot change the transactional state of the cache. Therefore, on a speculative load, the data is returned as normal but the transactional state is not affected. An additional request is sent to the cache when the transactional load graduates. When the non-speculative request hits in the cache, the target cache line is marked transactional. Although the additional request adds cache traffic, the effect is minimal since no data is returned.

An additional store request is not necessary since out-of-order processors like the MIPS R10000 generally do not speculatively issue store requests. Instead, store requests are only issued at instruction graduation when the instruction is no longer speculative. Therefore, when a transactional store request hits in the cache, the target cache line is marked transactional immediately. Some processors, however, issue store prefetches once the store address has been calculated. The prefetch simply brings the target line into the cache but leaves the data unchanged. Like speculative load requests, these prefetches do not affect the transactional state in the cache.

After a cache line is marked transactional, it remains transactional until the transaction commits. In the absence of overflows, simply clearing all the T bits commits the transaction. Clearing the T bits makes the once transactional cache lines visible in global memory since future cache interventions will cause the new values to be written back to memory. Transaction commit takes only one clock cycle since the T bits can be flashed cleared.

## Design rationale

The cache is used as the primary storage for transactional data since it introduces low performance overhead and requires only minimal changes to existing hardware. As shown in the Herlihy and Moss design, using the cache in this manner results in negligible performance overhead. This low overhead is expected since the cache mechanism does not fundamentally affect the processor pipeline or other hardware components in the critical execution path. The code is simply executed normally except transactional operations mark the cache.

Using one bit per cache line and one bit per cache set does not add much hardware overhead. In the MIPS R10000 with 128 byte cache lines, the overhead is less than 1.3% additional bits per cache line. There is also the added complexity associated with the ability to flash clear transactional bits in one cycle. Fortunately, these operations can be achieved by using additional global bit-lines connected to the modified SRAM cells used to store the state bits.

Issuing each transactional load twice generates higher cache traffic. The second request, however, is necessary since the UTM cache cannot store transactional state for instructions before graduation. Alternatively, speculative instructions could be allowed to mark the cache. Unfortunately, this alternative requires more complicated hardware since the cache must be unmarked if the speculative instruction does not graduate. Therefore, UTM issues transactional loads twice to simplify cache modifications. Further, as shown by results in Section 5.2 the additional cache traffic should not decrease performance drastically since no return data is required.

## 4.4 Transactional state in main memory

UTM overflows transactional data into a hash table in main memory if the cache limit is reached. Unlike previous systems which only used the cache to store transactional data, UTM allows transactions to grow effectively without bound. Since the hash table is in main memory, UTM incurs an additional performance overhead. The performance loss, however, is reduced significantly since all operations on the hash table take constant time. In this section, I describe the overflow hash table in detail.

The hash table in main memory is set up by the operating system but maintained by hardware. From the cache-coherency point of view, the hash table extends the cache. Although using main memory in this manner can potentially be slow, the overflow hash table will only be used rarely. In the common case, transactions fit in the cache and do not require overflow. Therefore, a slight performance decrease is acceptable since it can be efficiently amortized over the fast common case.

When the cache is about to evict a transactional cache line for capacity reasons,

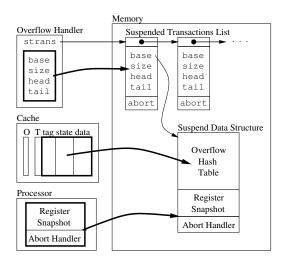

**Figure 4-2:** Speculative transactional storage in cache and main memory. The cache is the primary storage for speculative transactional data. When the cache is full, however, transactional data is overflowed into a data structure in uncached main memory. The overflow (O) bits indicate which cache sets have overflowed.